# ReRAM Compute ASIC Fabrication

DESIGN DOCUMENT sddec23-08 Client: Dr. Duwe Adviser: Dr. Wang Team Members: Joshua Thater, Aiden Petersen, Matthew Ottersen, Regassa Dukele sddec23-08@iastate.edu https://sddec23-08.sd.ece.iastate.edu/

Revised: 12/02/2023

# Table of Contents

| ı Te | am                                               | 3    |

|------|--------------------------------------------------|------|

|      | 1.1 Team Members                                 | 3    |

|      | 1.2 Required Skill Sets for Your Project         | 3    |

|      | 1.3 Skill Sets covered by the Team               | 3    |

|      | 1.4 Project Management Style Adopted by the team | 3    |

|      | 1.5 Initial Project Management Roles             | 3    |

| 2 In | ntroduction                                      | 4    |

|      | 2.1 Problem Statement                            | 4    |

|      | 2.2 Requirements & Constraints                   | 4    |

|      | 2.3 Engineering Standards                        | 5    |

|      | 2.4 Intended Users and Uses                      | 5    |

| 3 D  | )esign                                           | 6    |

|      | 3.1 Design Context                               | 6    |

|      | 3.1.1 Broader Context                            | 6    |

|      | 3.1.2 User Needs                                 | 7    |

|      | 3.1.3 Prior Work/Solutions                       | 7    |

|      | 3.1.4 Technical Complexity                       | 8    |

|      | 3.2 Design Exploration                           | 9    |

|      | 3.2.1 Design Decisions                           | 9    |

|      | 3.2.2 Ideation                                   | 9    |

|      | 3.2.3 Decision-Making and Trade-Off              | 10   |

|      | 3.3 Proposed Design During 491                   | 10   |

|      | 3.3.1 Design Visual and Description              | 10   |

|      | 3.4 How the Design Changed During 492            | -    |

|      | 3.4.1 Design Visual and Description              | _    |

|      | 3.4.2 Functionality                              |      |

|      | 3.4.3 Areas of Concern and Development           | -    |

|      | 3.5 Technology Considerations                    |      |

|      | 3.6 Design Analysis                              | .20  |

|      | 3.7 Design Plan                                  |      |

| 4 I  | mplementation                                    |      |

|      | 4.1 Implementation of Devices                    |      |

|      | 4.2 Implementation Issues                        |      |

| 5 T  | esting                                           |      |

|      | 5.1 Unit Testing                                 |      |

|      | 5.2 Interface Testing                            |      |

|      | 5.3 Integration Testing                          |      |

|      | 5.4 System Testing                               |      |

|      | 5.5 Regression Testing                           |      |

|      | 5.6 Acceptance Testing                           | . 28 |

| 5.7 Issues With ReRAM Simulation                                       | 29 |

|------------------------------------------------------------------------|----|

| 5.8 Results                                                            |    |

| 6 Project Outcomes                                                     | 30 |

| 6.1 Final 8x8 Compute Crossbar                                         |    |

| 6.2 GitHub Repository                                                  | 31 |

| 6.3 Post-Fabrication Bring-up Plan                                     |    |

| 6.4 Tutorial Documentation on Analog Design Flow + Other Documentation |    |

| 7 Closing Material                                                     | 32 |

| 7.1 Discussion                                                         |    |

| 7.2 Conclusion                                                         |    |

| 7.3 References                                                         |    |

| 8 Appendices                                                           |    |

| 8.1 Appendix 1 - Operation Manual                                      |    |

| 8.1.1 Pre-Fabrication Environment Setup                                |    |

| 8.1.2 Pre-Fabrication Tool Setup                                       |    |

| 8.1.3 GitHub Repository Cloning                                        |    |

| 8.1.4 Post-Fabrication Bring-up Plan                                   |    |

| 8.2 Team Contract                                                      |    |

# 1 Team

#### 1.1 TEAM MEMBERS

- Joshua Thater

- Aiden Petersen

- Matthew Ottersen

- Regassa Dukele

#### 1.2 REQUIRED SKILL SETS FOR YOUR PROJECT

- Willingness to learn and work together

- Strong persistence through challenging work

- Schematic editor

- Layout editor

- DevOps

- MCU programming

- PCB design

#### 1.3 Skill Sets covered by the Team

- Whole team

- Whole team

- Joshua Thater, Matt Ottersen

- Joshua Thater, Matt Ottersen

- Aiden Petersen

- Aiden Petersen

- Joshua Thater

#### 1.4 PROJECT MANAGEMENT STYLE ADOPTED BY THE TEAM

• We are going to use The Agile method with short 1 week sprints.

#### 1.5 INITIAL PROJECT MANAGEMENT ROLES

- Joshua Thater: Software tool researcher, mixed-signal designer

- Aiden Petersen: DevOps and digital designer

- Regassa Dukele: VLSI designer

- Matt Ottersen: VLSI designer

# 2 Introduction

## 2.1 PROBLEM STATEMENT

## Ideal:

- Iowa State University would have access to fabricated ReRAM chips for research purposes

- Iowa State University would have institutional knowledge of how the analog design flow works for the Skywater 130nm process

## **Reality:**

- It is difficult to get any fabricated chip, especially one with ReRAM, because of how new of a technology it is.

- Iowa State University has never produced a fabricated analog chip on the Skywater 130nm processed

# **Consequences:**

- It's difficult to do novel research that involves ReRAM because of the lack of fabricated chips.

- It's very difficult for students and faculty to create analog chips using the Skywater 130nm process because of the poor public documentation and the lack of internal documentation.

## **Proposal:**

- Use eFabless's MPW shuttle program to submit a ReRAM chip proposal.

- If it gets approved, it would give us access to fabricated ReRAM chips

- Along the way, we would document our workflow, contributing to ISU's internal knowledge of open-source analog chip fabrication in the SkyWater 130nm process.

# 2.2 Requirements & Constraints

# Functional Requirements (Specification)

- Create an eFabless MPW submission that contains a ReRAM crossbar that can be interacted with through the caravel harness.

- Crossbar must output higher whenever a single storage cell is in a LRS (low resistive state).

- Design must fit with the user project area  $(10 mm^2)$

- MPW Submission must pass eFabless pre-check.

- The crossbar will be interacted with through the wishbone bus, which is then turned into analog signals using a DAC and read back into the harness using an ADC.

- The ReRAM crossbar will be functional and able to perform multiple and accumulate operations.

- The ReRAM crossbar's inputs and weights will be assignable.

- Periphery analog circuitry must be designed to support crossbar computations. Some components that may be built include:

- 1-bit ADC

- 1-bit DAC

- Transimpedance amplifier

- 1T1R storage cell

- ReRAM crossbar

- MUXs

- Analog circuitry must be functional both at schematic and post-layout R+C extracted versions.

#### **Non-Functional Requirements**

- Document tools and tool flow necessary in the open-source analog design flow through eFabless.

- Create tutorial documentation on the open-source analog design flow. Include:

- Environment setup

- Required tools

- How the tools interact with each other

- How the tools integrate with the SkyWater 130 nm process

- Create a detailed post-fabrication bring-up plan that details how to test the chip and all of the different components located on it

- Create drivers that provide an API for programmers to interact with the crossbar.

## 2.3 Engineering Standards

**IEEE 1481-2019 - IEEE Standard for Integrated Circuit (IC) Open Library Architecture (OLA):** This standard fits our project since it goes over ways for our integrated circuit to be analyzed for timing and power consumption across a set of design automation (EDA) tools.

**IEEE 1076.4-2000 - IEEE Standard VITAL ASIC Modeling Specification:** This standard applies to our project since we will be designing an ASIC chip, and we will need it to test it with highly accurate and efficient simulation models.

**IEEE 1149.4-2010 - IEEE Standard for a Mixed-Signal Test Bus:** This standard will fit our project since it will house both analog and digital components, and we will have to thoroughly test all components both independently and together.

# IEEE 1364-2005 - IEEE Standard for Verilog Hardware Description Language: This

standard fits our project since we will have to write Verilog code that will communicate between the wrapper and the analog part of our project

#### 2.4 INTENDED USERS AND USES

The main intended user for the results of our project will be Professor Duwe and Professor Wang. They first want to test the potential computing power of a ReRAM crossbar. They also want to use our experiences and knowledge of our project to help future students design ASIC chips through the eFabless ecosystem, whether it be for research or in pursuit of creating a club for chip fabrication. Another user would be potential future students who are interested in analog/mixed-signal chip fabrication. It is our hope that they will be able to use our project as either an example or a jumping-off point for their own design. With the help of our documentation and written experiences, they should be able to hit the ground running when they want to work on fabricating their own chip through the eFabless process.

# 3 Design

#### 3.1 DESIGN CONTEXT

## 3.1.1 Broader Context

ReRAM is a non-volatile RAM that has the potential to perform computations in the analog domain. This can be beneficial as this requires less data movement and less power consumption as compared to typical computations done in the digital domain. Our project is to silicon prove a ReRAM crossbar using the SkyWater 130 nm process. We are hoping to tape-out this design and get it fabricated so that Professor Duwe and Professor Wang can evaluate the crossbar for computational potential. Outside of the two Professors, we are also designing for future students interested in open-source ASIC chip fabrication, as our project will help pave the way as an example. With our design, we are hoping that Iowa State will be able to create a curriculum or a club that is focused on the fabrication of chips. This will help the societal need of young engineers looking to get trained in the process of designing and fabricating ASIC chips.

| Area                                     | Description                                                                                                                                                                                                                                                                                                                       | Examples                                                                                                                                                                                                                                                                       |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public health,<br>safety, and<br>welfare | This project does not have a huge<br>impact on public health, safety, or<br>welfare. However, ASIC chips will<br>continue to have important uses in<br>many applications around the world<br>that do improve these areas.                                                                                                         | Our design will be added to the<br>open-source hardware in the<br>eFabless program, which may<br>lead to inspire or help other<br>engineers learn how to design<br>ASIC chips.                                                                                                 |

| Global,<br>cultural, and<br>social       | As this is an open-source project, we<br>are following the core ideals of<br>open-source development. These<br>include transparency, collaboration,<br>and continual growth. As such, our<br>project will follow these ideals and<br>will help pave the way for other<br>engineers to contribute to the<br>open-source community. | This project will add to the<br>open-source hardware<br>repository on the eFabless<br>website. Our design may be<br>used as a template for future<br>engineers, whether inside this<br>university or outside, as a<br>potential template for future<br>ReRAM crossbar designs. |

| Environmental                            | <b>ReRAM</b> has the potential to consume much less power than its digital                                                                                                                                                                                                                                                        | Our project will be<br>implementing a basic ReRAM                                                                                                                                                                                                                              |

|                                          | counterparts. There are many                                                                                                                                                                                                                                                                                                      | crossbar. This ReRAM will have                                                                                                                                                                                                                                                 |

Relevant considerations related to our project:

|          | companies that are looking at<br>ReRAM and trying to gauge whether<br>or not it will be beneficial to their<br>designs in the future. If this design is<br>adopted, then there may be a<br>substantial improvement in power<br>consumption for RAM throughout<br>the world.                                                                    | the hopes of utilizing much less<br>power compared to other RAM<br>types of similar size and<br>computational power.                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Economic | As this is an open-source project, all<br>of the tools are completely free to use.<br>Along with this, there are similar<br>designs that have been created<br>through this open-source workflow as<br>well. These designs may lead to faster<br>innovation and may lead to<br>companies feeling the need to<br>innovate their designs as well. | As we are designing our project<br>through this open-source<br>workflow, all of our designs and<br>process will be free to view and<br>use for future use. |

Table 1: Broader Context

## 3.1.2 User Needs

Professor Duwe is interested in building up ISUs in house capabilities with open-source ASIC chip design. He currently has other teams in the past go through the digital design flow, but he has yet to have a team map out the analog design flow. He has tasked us with figuring out this process flow and documenting it out for future use here at ISU with potential students and researchers.

Professor Wang is currently doing research with ReRAM, and he wants to test the SkyWater 130 nm process ReRAM for computational potential and fabrication. He needs us to create this ReRAM crossbar through the eFabless program so that he can evaluate its potential in his future research.

Future students interested in ASIC chip design need a way to understand how to create chips through the open-source workflow because learning how to tape out chips before entering the industry is an important skill to have.

#### 3.1.3 Prior Work/Solutions

There are only a couple of similar designs on the market, but they are proprietary and may not allow for the types of testing that our client wants. There have been numerous research studies and papers into ReRAM, but they often don't focus on the periphery analog circuitry that is needed to do ReRAM computations. They also don't talk about the fabrication process of these designs. So, there is not a lot of outside documentation we can utilize for how to approach designing a ReRAM compute crossbar much less attempting to actually fabricate it. That means that much of our design is going to be left to us to figure out how to do it based on our understanding of ReRAM computation and the analog circuitry that would be needed to support it.

We have also looked through passed MPW submissions that contained ReRAM modules. Many of these submissions claim to have said ReRAM modules in them, but after cloning the repositories and checking the files, very few actually include ReRAM at all. There are a few that do include some ReRAM modules, but they are untested, and we don't actually know if they would work on a fabricated chip. They also seemed to not have a way to test the ReRAM module at the schematic level, so while there were some designs that included ReRAM, we decided it would be best to come up with our own design based on concept sketches we have found through a few research papers.

One of the research papers that we used to research ReRAM computation and the basic structure of the periphery analog circuitry:

[1] A. Shafiee et al., "ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars," 2016 ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), Seoul, Korea (South), 2016, pp. 14-26, doi: 10.1109/ISCA.2016.12. https://ieeexplore.ieee.org/document/7551379

Another research paper that was used to aid our research into ReRAM computation can be found here:

[2] T. Chou, W. Tang, J. Botimer, and Z. Zhang, Electrical Engineering and computer science, <u>https://web.eecs.umich.edu/~zhengya/papers/chou\_micro19.pdf</u>.

### 3.1.4 Technical Complexity

The design consists of both digital and analog circuit design. The components of the design include:

Resistive Ram Module

- This requires research into how resistive ram works

- Figuring out how to implement ReRAM into our design

- How to simulate this module by itself and with other components

#### ADC and DAC

- We will need to design Op-Amps with our preferred performance characteristics that will amplify signals and work as voltage shifters

- Knowledge of how to design ADC and DAC for specific applications

- How to integrate these designs together to work with the ReRAM crossbar

Use of open source tools

• Ability to learn, setup, and troubleshoot software/process flow that has little to no documentation

Creating a layout for the circuit that passes LVS and DRC

• This will require design knowledge and skills for ASIC chip design

One challenge is the theoretical implementation of ReRAM. This will require research of how ReRAM works and then designing a circuit that allows a system to ReRAM effectively. Then, the next challenge comes through having to bring that design to silicon by using an open-source design process. This will be complex as the open-source analog process flow we are using has very little documentation on how to bring design through the process.

#### 3.2 DESIGN EXPLORATION

#### 3.2.1 Design Decisions

Our design has many circuit components in it, and all of these components have multiple ways to be implemented. One of the key design decisions we made was what type of DAC would be used to pipe the digital voltages (high or low) to analog voltages so that the ReRAM crossbar would compute in the analog domain. We landed on doing a simple DAC architecture of a buffer, which is just 2 inverters cascaded together. This will work for our design is it will allow us to take in a voltage and shift it to whatever voltage is supplied to the VDD of the buffer.

Another key design decision we made was the architecture of the ADC. Just like with the DAC, we need a way to convert between analog and digital realms. For this project, we need a way to convert the analog computations back to a digital value to be read. The next 2 sections detail our design decision for this crucial component.

One last key design decision we made was how we were going to load weights onto the ReRAM cells. We have decided that we are going to use the logic analyzer pins provided to us on the Caravel Harness. However, these pins only output 0 V or 1.8 V, while our ReRAM crossbar will need varying voltages. To get these varying voltages we will use level shifters and our DAC. The level shifters, which will be voltage dividers, will take the power supply voltage and reduce it down to the needed voltages to the VDDs of DAC that will then feed into the ReRAM crossbar.

#### 3.2.2 Ideation.

For data converter architectures, there are many options to choose from. Specifically for ADC converters, there are almost too many options to choose from. Each of these options comes with its own benefits but also its own drawbacks. One ADC may be faster but less accurate, while another may be able to do more complex conversions. So, picking the architecture for our ADC was important as we wanted it to be able to best match the needs of our project. From our research, we found that there were five main architectures that are widely used. These architectures were:

- Successive Approximation (SAR) ADC

- Dual-Slope ADC

- Pipelined ADC

- Flash ADC

- Delta-Sigma ADC

# 3.2.3 Decision-Making and Trade-Off

In order to choose which architecture to use, we weighed the pros and cons of each. After some research, we created this table:

| ADC Architecture | Pros                                                                              | <u>Cons</u>                                                                           |

|------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| SAR              | Handles waveshapes very<br>well, takes very high sample<br>rate, high resolutions | Can be slow, larger/more<br>complex design at low<br>resolutions                      |

| Dual-Slope       | Very accurate, and has high-resolution                                            | Slow sample rate and speed, can be hard to implement                                  |

| Pipelined        | Very fast speeds, good resolution                                                 | Inherent latency due to architecture                                                  |

| Flash            | The fastest speed, no latency,<br>easy to implement at "1-bit"<br>level           | Circuit gets much bigger with<br>resolution increases, limited<br>to 8-bit resolution |

| Delta-Sigma      | Very high resolution, reduces quantization noise                                  | Limited sample rate, does not handle unnatural waves                                  |

Table 2: Decision Making for ADC Architecture

As can be seen from this table, each architecture comes with its own pros and cons. For our project, we are only using a 1-bit ADC, so we do not care about resolution. We also want something that is relatively small and easy to implement, as this circuit will be copied and pasted for the 8 columns that our crossbar will have. Because of all of this, we went with the flash ADC. While it can get larger with more bits, since we are only using it for 1-bit conversions, this will not be a concern. We also chose this one because of its fast speed, low latency in conversions, and because it is relatively simple to implement in a 1-bit form.

We also needed to choose from which type of ReRAM cell we were going to use. We decided on using 1T1R (1 transistor 1 resistor) since it had the most information available about it in the research papers we used to base our designs off of, and it suited our needs. There were also 1 transistor multiple resistors, 1 selector 1 resistor, and 1 diode 1 resistor options, but we decided not to use these.

#### 3.3 PROPOSED DESIGN DURING 491

# 3.3.1 Design Visual and Description

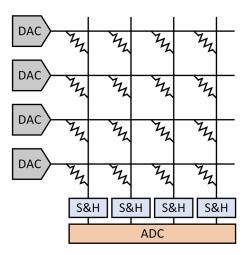

The figure below shows a basic ReRAM crossbar with analog circuitry around it that allows for a digital value to be input and a digital value to be output from the analog computation.

Figure 1: ReRAM Crossbar High-Level Diagram [2]

The figure above shows the basic top-level schematic of how we will create our design to test the ReRAM crossbar for computational potential. First, we input digital values into the DAC. As they go through the DAC, the digital values are converted into analog voltages, which go through the ReRAM crossbar. At each column of the crossbar, current will accumulate, depending on the state of the crossbar and the digital values inputted. At each column, a transimpedance amplifier will be placed so that we can convert the current back to a voltage. Once that voltage is obtained, it will go through a sample and hold circuitry (S&H) and then be converted back to a digital value through a 1-bit ADC. This digital value is then inputted back into the Caravel harness to be read. This is called a MAC operation, and a simplified version of it is shown below. The input voltage is multiplied by the conductance of the ReRAM which gets accumulated on the column.

Figure 2: MAC Operation [2]

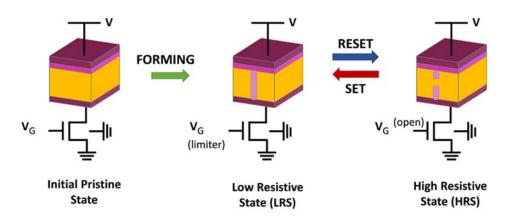

The conductance of a ReRAM cell is changed depending on whether it is in an LRS (low resistive state) or if it is in an HRS (high resistive state). If it is in an LRS, it can be interpreted as a "digital 1" as the cell will be on. If it is in an HRS, it can be interpreted as a "digital 0" as the cell will be off. By setting these different cells to different states, we can perform complex computations. The figure below shows an illustrative way to understand this idea.

Figure 3: ReRAM States [3]

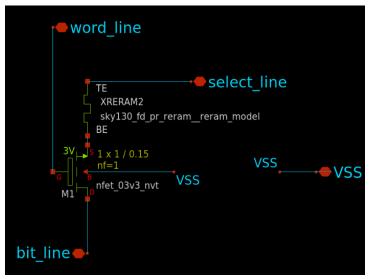

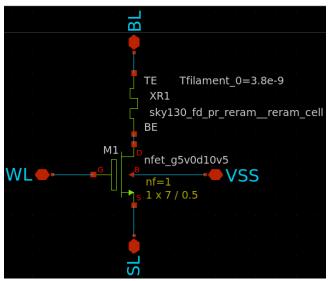

The figure below shows what one cell of the ReRAM (1T1R cell) crossbar will look like.

Figure 4: 1T1R Cell

As is seen in the figure, the cell consists of the ReRAM and a transistor. Thus, it is named a 1T1R cell. The gate of the transistor is going to be attached to the logic analyzer of the Caravel harness, which will write a weight to it. In the overall circuit, we will write the weights for an entire row of these cells at once. The select\_line will be what is inputted into the cell. So, that means that the output of the 1-bit DAC will go into the select\_line. Finally, the output of the cell will be the

bit\_line which will accumulate current. These currents will be added to the currents of other cells along that column that will then be converted to a voltage.

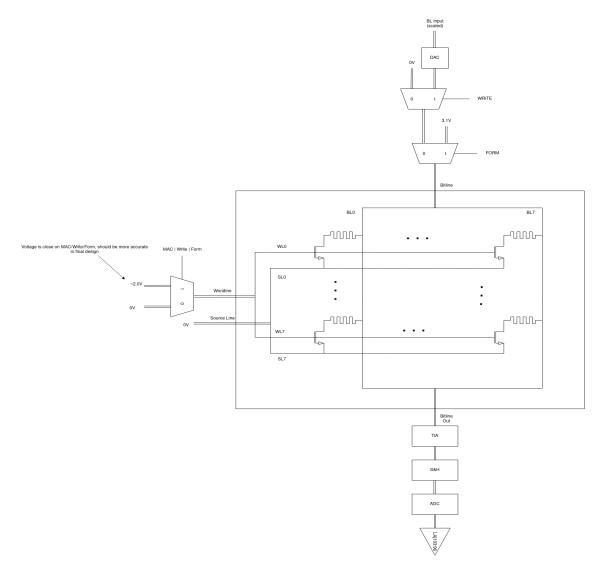

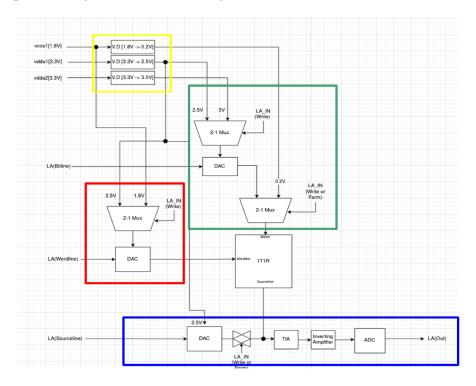

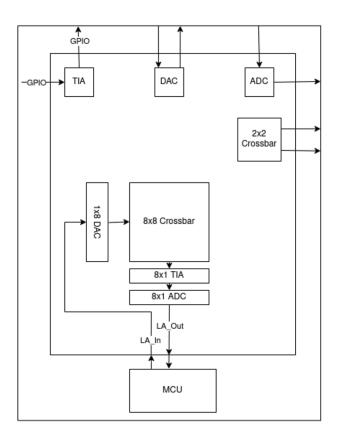

The figure below shows our whole system and how it will be integrated with the Caravel harness infrastructure:

Figure 5: User Area Top Level Diagram

#### 3.4 How the Design Changed During 492

## 3.4.1 Design Visual and Description

Throughout 492 our design has changed quite a bit based on our changing understanding of the limitations of the Caravel Harness. We also have simplified the design so that it would be easier to implement during the layout process. While we have changed our top-level design, the overall

idea of how we perform calculations remains the same. We will still take in voltages from the logic analyzer and shift them to the needed voltages that will be input to the crossbar depending on what operation is occurring. The table below comes from the SkyWater documentation for the ReRAM module we are using and shows the recommended voltages for the different write operations that are needed for ReRAM.

| 1T1R #5  | WL (V)                  | BL (V)                  | SL (V) | PW (ns) | Yield (%) |

|----------|-------------------------|-------------------------|--------|---------|-----------|

| Pristine |                         |                         |        |         | 99.90     |

| Form     | 1.4 - 2.0 (0.1<br>step) | 2.6 - 3.1 (0.1<br>step) | 0      | 1000    | 92.73     |

| Reset    | 2.5                     | 0                       | 2.6    | 1000    | 90.83     |

| Set      | 1.7                     | 2.4                     | 0      | 1000    | 97.45     |

Figure 6: Table for Recommended Voltages for ReRAM Operations [4]

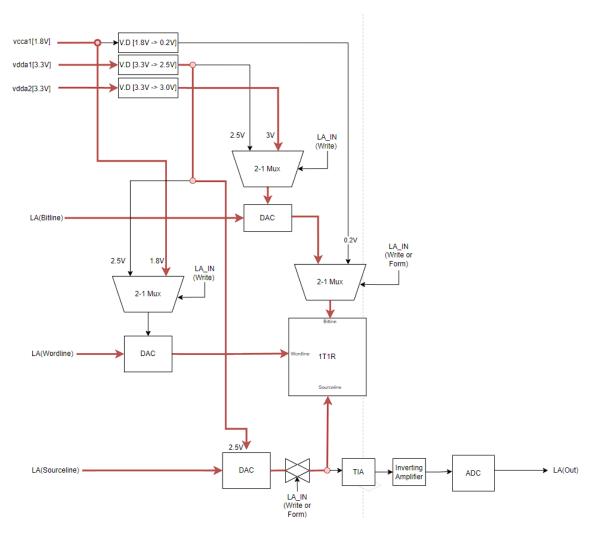

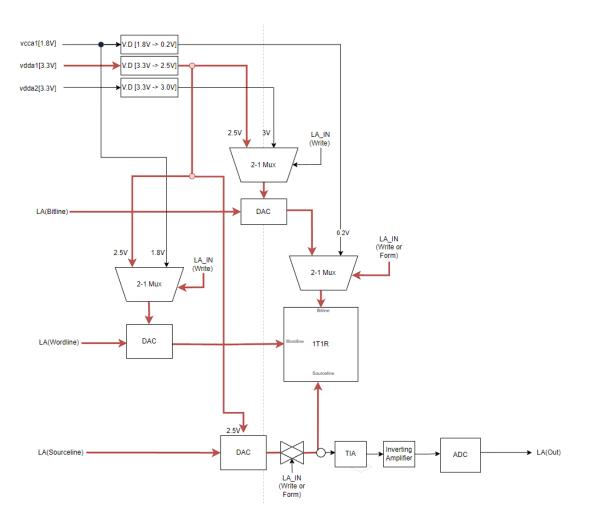

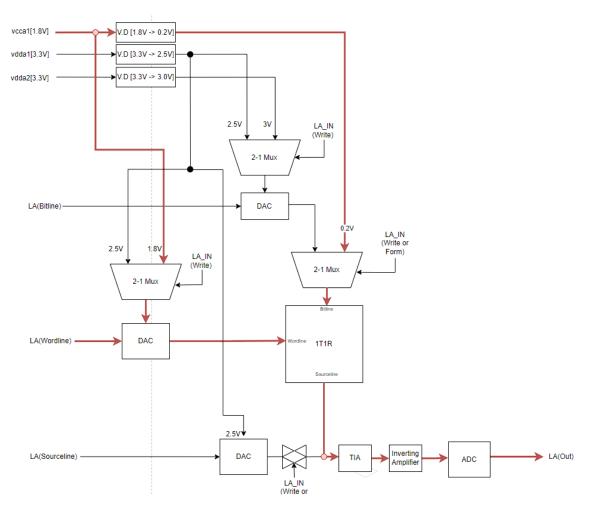

So, using the information in this table we will use the level shifters (voltage dividers) to supply the correct voltages for the VDDs of DAC. These DACs will then input the correct voltages into the crossbar. From there once we have written the crossbar, we will then do computations on it, where we will input a voltage which will be multiplied by the conductance which will then accumulate current on a column. These accumulated currents will then be converted back to a digital voltage through a transimpedance amplifier, inverting amplifier, and 1-bit ADC. Our updated top-level design can be seen in the figure below.

Figure 7: Updated Top-Level Design

The circuits that are enclosed in the yellow box are our level shifters. These will take the different power voltages supplied by the Caravel Harness and shift them down to the needed voltages for the crossbar. The circuitry in the green box is the bit-line. In the red box is the circuitry for the worldline. Finally, the blue box encompasses the select line circuitry. We also got rid of the sample and hold circuit as we realized that it is not needed for the 1-bit ADC we are using. It should also be noted that we changed the 1T1R cell slightly for this updated design. The updated 1T1R cell is shown in the figure below.

Figure 8: Updated 1T1R cell

In this updated design, we have switched where the bitline and selectline are. This is because we changed which side of the 1T1R cell we will output current from. After doing some more reading during this semester we realized that it was pretty interchangeable which side of the cell you outputted current from, so we decided to switch it to this orientation.

With our updated design we were also able to do all of the needed operations (form, write, read, MAC) which was not clear with the previous design. The figures below show how the voltage travels through our design to do the different operations.

Figure 9: Form Operation

The figure above shows the form operation. This operation will need to be done so that we can do all other operations on the crossbar. The bitline is being supplied 3 V, the worldline is being supplied 1.8 V and the select line is inputting 0 V (LA(Souceline) is supplying a 0 V input, so even though the VDD of the DAC is 2.5 V, only 0 V go through).

Figure 10: Write Operation

The figure above shows the write operation. In this operation, the ReRAM storage cell is either "set" (LRS) or "reset" (HRS). In this operation the worldline is getting 2.5 V is that row is being written to. If it is not being written to it will be supplied 0 V. The bitline is getting 0 V or 2.5 V depending on if it is "resetting" or "setting" respectively. The selectline is getting 2.5 V or 0 V depending on if it is "resetting" or "setting" respectively.

Figure 11: Read/MAC Operation

The figure above shows the read/MAC operation. Specifically for the MAC operation 0.2 V is supplied to the bitline, 1.8 V is supplied to the worldline and the summed current goes through the transimpedance amplifier, inverting amplifier, and ADC to the logic analyzer. During the read operation the worldline is toggled to 0 V or 1.8 V depending on if that row of cells is being read.

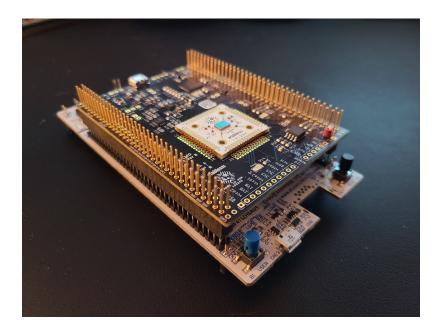

#### 3.4.2 Functionality

Once our design is fabricated, a user will have our ASIC chip printed out on a board with numerous controls that are dictated by the Caravel Harness. This board is provided in the fabrication process through the eFabless program. The user will be able to select digital inputs that they want to input into the chip to be computed by the ReRAM crossbar. They may also want to write weights to the ReRAM crossbar, which they will also be able to do with the circuitry around our chip. Once they input the values, they will then be able to read the digital output of these values on one of the output pins of the board. This design will meet all functional requirements of the ReRAM crossbar, as values will be able to be input and weights will be able to be written to the cells.

# 3.4.3 Areas of Concern and Development

The primary concern of our project is fully instating all of the analog devices that will be used in this project and getting them past precheck. For each analog device, we will have to create a schematic, simulate that schematic, create a layout of that device, and pass DRC and LVS tests on that layout. Once we have that done for each component, we have to create a top schematic and run through everything again. Once that is done, we have to connect everything up in the analog wrapper that is provided by eFabless and try to pass precheck. As can be seen, by this description, there are a lot of steps, and that means a lot of places where things can go wrong or get bottlenecked for some time in our design. We will attempt to address this concern by being proactive and working ahead of schedule. If we run into any trouble, we will use a Slack channel that is used for open-source chip design for help.

#### 3.5 TECHNOLOGY CONSIDERATIONS

Simulators:

- Ngspice

- Better integrates into eFabless framework

- Easier to setup

- Cannot simulate VerilogA well, but has support that can make it easier

- Xyce

- Harder to setup (need to configure it properly)

- Is able to simulate VerilogA

- Requires other software (Trilinos)

- None of our components other than ReRAM have VerilogA netlists

For our simulator we chose Ngspice because most of our components have Spice netlists, so it is much easier and faster to simulate with it. The only hard part comes with simulating the VerilogA netlist of the ReRAM device. Luckily for us during the time of this project, Ngspice received an update that allowed it to do simulations on VerilogA netlists.

User area communication:

- Logic analyzer

- Easy to use

- Easy to implement for hardware

- Has 128 bits

- GPIO

- Can communicate with user area using configuration

- Not very many available communication bits

- Wishbone

- More flexible, follows a standard

- Difficult to implement

- Hard to do a handshake with analog circuitry

We decided to use the logic analyzer because it allows for us to place more components in the user area for our design. We also wanted to reserve the GPIOs for external characterization of our analog devices along with a smaller ReRAM crossbar.

#### 3.6 DESIGN ANALYSIS

Our design is a great prototype for how periphery circuits interact with a ReRAM crossbar. Our design is theoretically able to supply all the needed voltages to the crossbar to perform all of the needed operations. We should also be able to perform both read and MAC operations with this design. This design should be able to scale up to as large as a crossbar as is required, so long as the layout area can fit it. If this design is fabricated we hope that it will show that not only does our design work, but that ReRAM computation can be achieved through fabrication with the SkyWater 130 nm process.

That is not to say that our design is perfect. There could be many improvements made to it. From our work, a future team can make a more complex design, such as having a more complex ADC to remove quantization effects or by including decoders/encoders to do computations at a much faster rate. They may also be able to improve upon the footprint of our design, finding ways to make this process more robust or easier to layout on silicon. Overall, our design is a great first step towards figuring out ReRAM computation through the open-source analog design flow through eFabless using the SkyWater 130 nm process.

#### 3.7 DESIGN PLAN

Our design plan is to design and test all analog components individually. Once we have verified that the individual components meet our functional requirements (this includes testing of the extracted post-layout results), we will move to testing the functionality of the individual components when put together. The goal of this is to ensure that the functionality of one device will not interfere with the functionality of another device. If we notice that there are undesired results when we simulate multiple components together, we will tweak the components until we do get the desired results. Once we have verified that all components work together, we plan on creating a top-level layout and hooking up the Caravel harness. Once our circuit is hooked up to the Caravel harness, we will run multiple test cases to ensure the functionality of our circuit still remains intact when hooked up the harness.

Going through this design plan should ensure that we meet all requirements of our project. We will be able to show the functionality of our circuit when not hooked up to the Caravel harness and when it is hooked up to the harness. With our layout, we will ensure that all DRC and LVS tests are passed so that our design will be able to pass precheck. With all of these parts of our design plan, we should be able to meet the goals of this project and successfully tape-out or design.

# 4 Implementation

#### 4.1 IMPLEMENTATION OF DEVICES

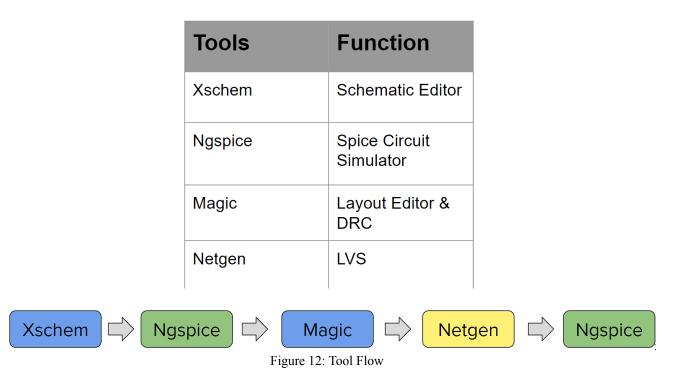

In order to implement our design we must go through the open-source analog design flow that is required by eFabless. This took quite a while to figure out as there is little to no documentation on it. However, the basic tool flow is shown in the figure below.

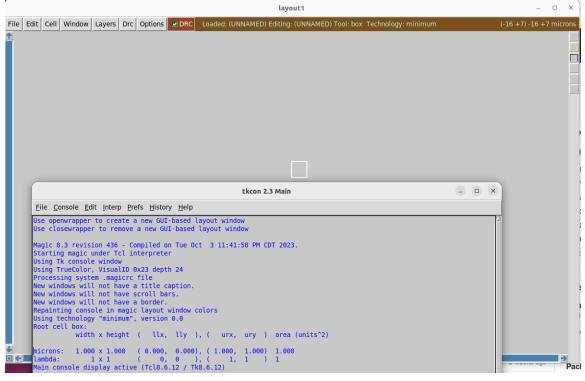

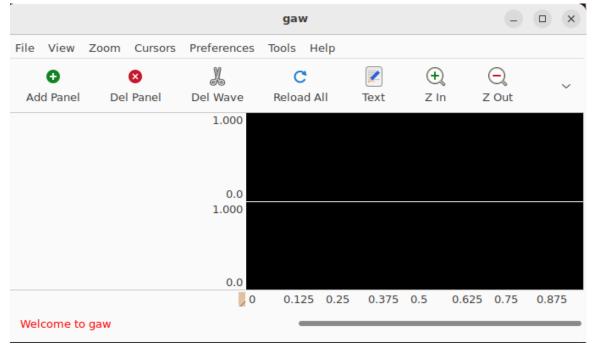

In the analog design flow, we start off in Xschem which is a schematic editor. In this tool, this is where we create our schematics at a transistor level. These transistor models are provided to us through the SkyWater 130 nm process. Once we have created our schematic and sized the devices in it we move on to the next tool which is Ngspice. Ngspice allows us to simulate the netlists of our schematics. This tool allows us to run different simulation tests on our designs. We will then plot the waveforms and see if the results match our expectations.

Once we have verified that our schematic behaves the way we expect it to, we then move over to Magic which is the layout editor. This will allow us to layout our design and how it would actually be fabricated on a chip. In this tool, we create our layouts and run a DRC (design rule check) to ensure that our design can actually be fabricated without failing any fabrication rules (such as two nets being too close together). From Magic, we then use Netgen to compare the netlists generated by our schematic level design and our layout level design in an LVS (layout vs. schematic) check.

If this passes, we then extract an R+C version of the netlist generated from the layout. This extracted netlist attempts to incorporate the different resistances and capacitances that will exist in a design once fabricated. We then pop this back into Ngspice and run a post-layout simulation on

it to see if the parasitics that were created hamper the behavior of the design. If after the post-layout simulation, the design still behaves as expected, then that design is finally implemented through the open-source analog design flow. A theoretical design may have to go through this entire process again if it does not behave correctly when implemented with other designs.

If this sounds like a lot of steps, that is because it is. It should be noted that for every design we did we had to go through this process at least once. The designs that we pushed through this design flow include:

- Inverter

- Buffer

- Transmission Gate

- 2-1 MUX

- 4-1 MUX (not used in final design)

- 1-Stage Operational Amplifier

- 2-Stage Operational Amplifier (not used in final design)

- 1-bit ADC

- 3-bit ADC (not used in final design)

- Transimpedance Amplifier(s)

- Inverting Amplifier

- Level Shifters

- ReRAM Device

- 1T1R cell

Some of these designs we did not end up using for varying reasons, such as realizing that we didn't end up needing them or that they were not fully implemented in time once system level design began.

Once we had these devices created through this design flow, we had to put them together so that we could hook them up to the Caravel Harness in layout. A rough concept sketch of how we would do this is shown in the figure below.

Figure 13: Concept Sketch of Desing Hooked up To Caravel Harness

We would hook up our compute crossbar to the logic analyzer pins on the Caravel Harness and we would hook up individual components/a smaller crossbar to the GPIOs for external characterization. We also did this as a risk mitigation method in case our design didn't work once fabricated, we would at least have external circuits we could test to ensure that actual designs can be fabricated using the SkyWater 130 nm process. We also included a smaller 2x2 so we could do our own individual characterization of it.

To create this layout, we created an 8-line version of the worldline, bitline, select line, and the 8x8 ReRAM crossbar independently. We then hooked up all of these components together before finally hooking all of them up to the Caravel harness. We also created a second version of the compute crossbar for a different read/MAC voltage to be placed in the layout as well. We did this so that we could further risk mitigate our possible fabricated design. The only difference between the two was the 8-line selectline output that had a different-sized transimpedance amplifier to account for the different read/MAC voltage. Once crossbar was for a 0.2 V read/MAC and the other was for a 0.4 V read/MAC.

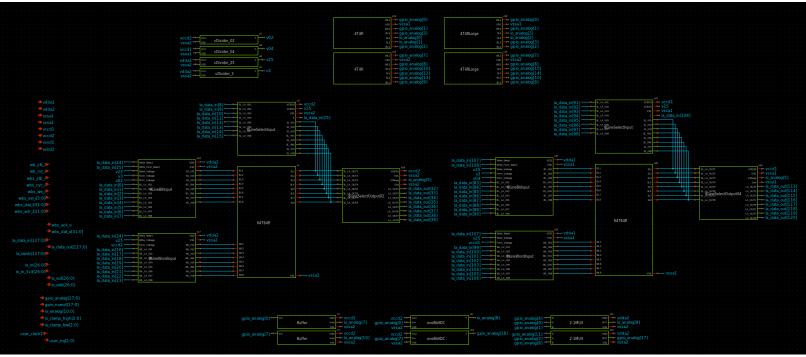

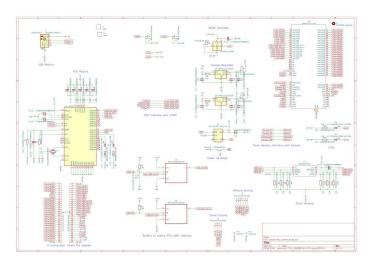

After we had hooked both of these up we hooked up all of the individual components on the side and connected them up to the GPIOs. Once this was all finalized we had successfully created the layout of our final design. The schematic level hook-up of our final design is shown in the figure below (you may have to zoom in on it as it is a massive picture).

Figure 14: Schematic Level View of Hook-up to Caravel Harness

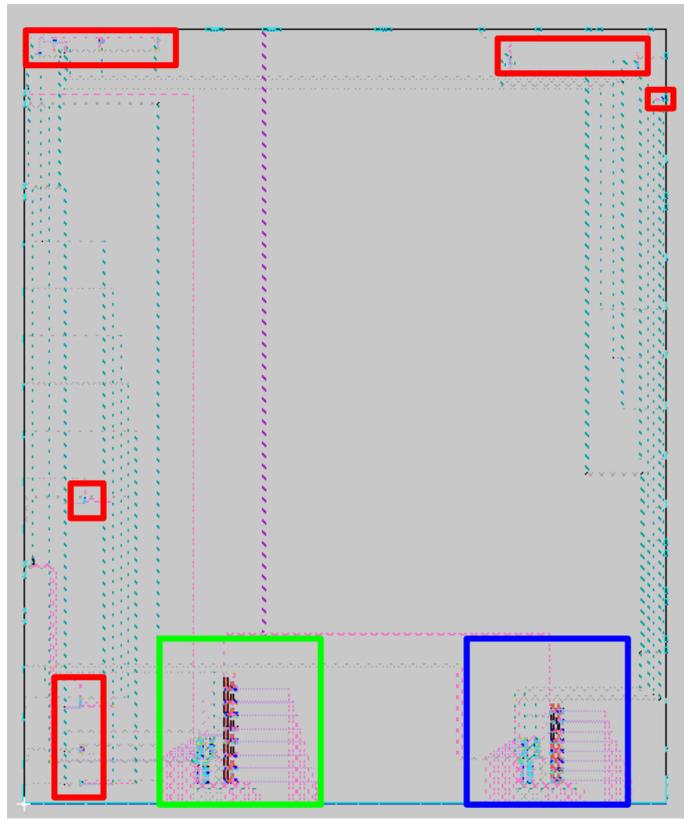

The actual layout of our design with all of the components can be found in the figure on the following page.

Figure 15: Layout Level View of Hook-up to Caravel Harness

The layout area is massive, so it is hard to grab an all-encompassing picture that highlights all of the devices and connections. The stuff in the green box is the 0.2 V compute crossbar, in the blue box is the 0.4 compute crossbar, and the red boxes show where the external circuitry is that is connected to the GPIOs.

#### 4.2 IMPLEMENTATION ISSUES

Unfortunately, with our final design, we were not able to pass an LVS check. There are two reasons for this. The first reason is that we connected the substrate of our PMOS devices to multiple different pins. This is an issue because this substrate is a singular layer meaning that it can only support one voltage level. When we have multiple different pins connected to it, the program assumes that they will be connected to different voltages, so it does not match the schematic netlist. The way to fix this is to isolate the substrate of the PMOS devices so that each device can get its respective voltage/ground. However, we were not able to figure this out in time, but it does look like it is possible with the SkyWater 130 nm process.

The other reason that it does not pass LVS is because of the ReRAM device itself. As this whole process is essentially in "alpha," things are still being worked on and developed. One of those things is the ReRAM device. In its current state, it is unable to pass an LVS check due to netlist errors that arise from Xschem and Magic. This is due to the developer of Xschem having to write special model statements in the netlist of the ReRAM cell to get it to function properly with Ngspice. However, these model statements do not get extracted to Magic, and so LVS fails as it can not properly compare the two netlists.

We also attempted to take a 1T1R cell through precheck to see if that is possible, but as of the time of writing this, it is not. This is because of the updated model of the ReRAM not being able to pass LVS, and thus it fails precheck with an error. We have been in contact with the developers of these tools and the people at eFabless themselves and they are currently working on a fix.

# 5 Testing

#### 5.1 UNIT TESTING

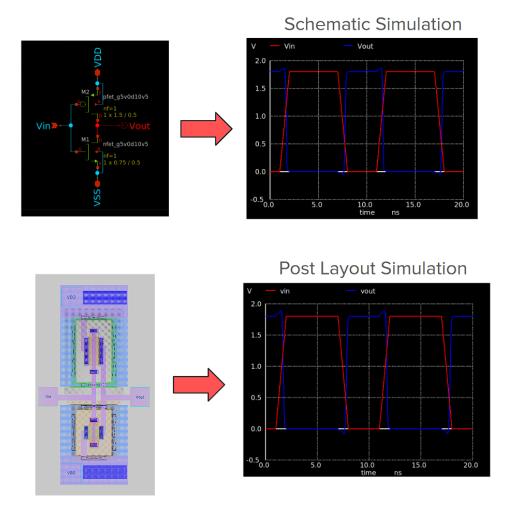

Our design will consist of many units. The main units will be the analog circuitry, such as the DACs, ReRAM cells (1T1R), transimpedance amplifiers, and ADCs. These units will be thoroughly tested using the open-source tools we have available to us. For each device, we will have to make a schematic of it using XSchem. From that schematic, we will then create a testbench in Xschem to observe its behavior. These testbenches will be simulated using Ngspice or Xcye. Once we have verified if that device meets our design requirements and expectations, we will then have a layout created for it using Magic. We will then obtain the post-layout parasitics using Magic and simulate that parasitic netlist using Ngspice. An example of what this would look like is shown in the figure below for the inverter design.

Figure 16: Example Unit Testing on Inverter

# 5.2 INTERFACE TESTING

The interface between each of our components will be wires. The number and name of the wires will vary based on what is needed from them. In our project, we have a user area which needs to be communicated with via a RISCV CPU. This communication will be done over a configurable 128bit logic analyzer. Whether each bit is an input or output is configurable.

The composition of multiple units is being tested the same way as individual components, which is creating testbenches in XScehm, simulating through Ngspice, creating a layout using Magic, verifying LVS, and extracting parasitics to rerun simulations with.

# 5.3 INTEGRATION TESTING

The main integration path in our design comes from the connection of all of our analog components to the outside Caravel harness. This path is fairly linear when we are computing data. Digital data will be entered into our circuit from the Carvel harness, where our chip will do computations in the analog domain before returning a digital value back to the harness. Before

hooking up our circuit to the Caravel harness, we will ensure that the analog circuitry is behaving as expected. This will be done by creating a top-level schematic of all the components connected together in Xschem. We will then create a testbench that simulates the behavior of this circuit. This testbench will simulate the conditions that the circuit will be in when connected to the Caravel harness. We will run these simulations using Ngspice. Once this is done, we will use Magic to connect together all of the components and extract post-layout parasitics. We will then simulate these parasitics, and if the results are still acceptable, we will move on to connect our circuit to the outside harness. We will run further testing on this to ensure that everything still behaves as expected.

#### 5.4 SYSTEM TESTING

This part is awkward; unlike with fully digital designs, we are unable to fully verify our product. We must test in two separate parts. We currently have a fully functional digital implementation of our project, which has the same behavior as the ReRAM crossbar, so it demonstrates the same functionality in digital simulation. The fully digital simulation allows us to determine if our port mappings are going to work, along with if our drivers will work.

For the second part, we need to determine if our analog ReRAM crossbar component's behavior matches our digital implementation. This must be done through analog simulations since it uses analog components. Our strategy here consists of writing many top-level tests to ensure all of the operations are working.

#### 5.5 REGRESSION TESTING

The testing will be very iterative to ensure that everything works properly together. In our design, we need to make sure that each unit works not only independently but they all work together. For this regression testing, we will first build and simulate a schematic of each individual unit to ensure it works as intended using Xschem. Next, we will hook up two units together that will be connected in our final design. For example, we will hook up the 1-bit DAC with the 1T1R cell. We will then create a testbench and run simulations using Ngspice to view how they behave together. If we observe that they are not behaving as expected, we will have to tweak the individual components and run simulations until they do behave as expected. Once we have verified that the two components work together, we would then connect one more component and run through the same process again. We would repeat this process until all components have been connected and simulated with acceptable results. Running through the testing this way, we can ensure that all components will work together, but it will also allow us to have an easier time troubleshooting if something deviates from the expected behavior, as we will be able to identify the component that is causing the problem.

#### 5.6 ACCEPTANCE TESTING

Our design will be tested for non-functional acceptability through the precheck process the eFabless uses to verify that our design meets certain requirements. Some of these prechecks include DRC and LVS checks. This precheck essentially runs multiple DRC checks to ensure that our layout does not violate any rules and is able to be fabricated on silicon. For the functionality,

we will have to run simulations and test cases on our design to verify that it behaves as expected. These simulations will be done using Verilog to simulate how our circuit will operate within the Caravel harness. From these simulations, we will obtain waveforms that will help verify the functionality of our chip.

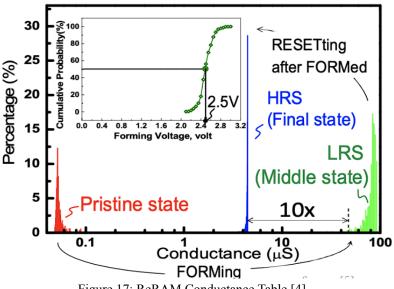

#### 5.7 ISSUES WITH RERAM SIMULATION

As was mentioned earlier, the current ReRAM model is currently still being developed and tested in this open-source design flow. As a result of this, simulations are currently not able to be done with anything other than the model by itself - and even then, it is not reliable. So when we attempted to do simulations on a 1T1R cell, the simulation failed due to convergence issues. We have informed the eFabless team, and they seem to be working on making it better for the future. In the meantime, we still had to try to do simulations. Luckily for us, the SkyWater documentation has a section on ReRAM characteristics and it shows a graph of the ReRAMs conductance during its different states. This figure can be seen in the figure below.

Figure 17: ReRAM Conductance Table [4]

Using this table we were able to simulate the different states of the ReRAM with a regular resistor by converting the conductance to a resistance and sizing a transistor to match that.

#### 5.8 RESULTS

We were able to test and verify that all of our individual analog circuitry worked as intended. We were also able to push all of them successfully through the analog design flow (with the exception of ReRAM stuff not passing LVS). Once we had done that, we hooked up our design in a top-level schematic and ran simulations on that. For form and write operations we were able to verify that the needed input voltages could get to where they needed to get to. There may be some issues with the loading effects of the resistances impacting the voltage that arrives. It did not seem to be a huge issue for the lower voltages, but as the voltage increased, the more the difference in expected vs. actual voltage differed.

For read/MAC operations, we had to do some estimation of the ReRAM as was explained in section 5.7. As a result of this, we also did some error testing by doing "minimum conductance" and "maximum conductance" tests. Since the LRS varies quite a bit in conductance, we grabbed a minimum conductance of 80 uS and a maximum conductance of 100 uS. Along with this error testing, we also did corner testing to see how/if that affected the results of our computations. Finally, we did all of these tests for both the 0.2 V and 0.4 V versions of the compute crossbar. The figure below shows some tables of the results of these tests.

| At 0.2 V. 80 uS   |                   |      |           |           |            |          | At 0.4 V. 80 uS   |                   |      |           |           |            |          |

|-------------------|-------------------|------|-----------|-----------|------------|----------|-------------------|-------------------|------|-----------|-----------|------------|----------|

|                   | # of cells in HRS | TEST | BL In (V) | SL In (V) | InvOut (V) | Vout (V) | # of cells in LRS | # of cells in HD9 | TEST | BL In (V) | SL In (V) | InvOut (V) | Vout (V) |

| 0                 |                   | TT   | 0.1879    | 0.0592    | 0.4692     | 0.0057   | 0                 |                   | TT   | 0.3694    | 0.7192    | 0.429      | 0.0226   |

| 0                 | _                 | SS   | 0.1847    | 0.0578    | 0.4557     | 0.0039   | 0                 | _                 | SS   | 0.3613    |           |            | 0.01328  |

| 0                 |                   | FF   | 0.1901    | 0.0602    | 0.4795     | 0.0077   | 0                 | -                 | FF   | 0.3749    | 0.7293    | 0.4394     | 0.03421  |

| 0                 | 8                 | FS   | 0.1843    | 0.0595    | 0.4509     | 0.0039   | 0                 | 8                 | FS   | 0.3602    | 0.7223    | 0.4208     | 0.01415  |

| 0                 | 8                 | SF   | 0.1898    | 0.0583    | 0.4775     | 0.0075   | 0                 | 8                 | SF   | 0.3754    | 0.7062    | 0.4421     | 0.03053  |

| # of cells in LRS | # of cells in HRS | TEST | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) | # of cells in LRS | # of cells in HRS | TEST | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) |

| 1                 | 7                 | π    | 0.1804    | 0.1203    | 0.7049     | 1.784    | 1                 | 7                 | ττ   | 0.3436    | 0.1818    | 0.7345     | 1.788    |

| 1                 | 7                 | SS   | 0.1749    | 0.1147    | 0.7064     | 1.787    | 1                 | 7                 | SS   | 0.3282    | 0.1684    | 0.7314     | 1.79     |

| 1                 | 7                 | FF   | 0.1846    | 0.1245    | 0.7057     | 1.778    | 1                 | 7                 | FF   | 0.3543    | 0.1919    | 0.7333     | 1.784    |

| 1                 | 7                 | FS   | 0.1746    | 0.1143    | 0.7165     | 1.789    | 1                 | 7                 | FS   | 0.3258    | 0.1668    | 0.735      | 1.792    |

| 1                 | 7                 | SF   | 0.1844    | 0.1247    | 0.6944     | 1.775    | 1                 | 7                 | SF   | 0.3555    | 0.1928    | 0.7255     | 1.781    |

| # of cells in LRS | # of cells in HRS | TEST | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) | # of cells in LRS | # of cells in HRS | TEST | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) |

| 8                 | 0                 | TT   | 0.1783    | 0.1666    | 0.772      | 1.789    | 8                 |                   | TT   | 0.3315    | 0.2987    | 0.8189     | 1.793    |

| 8                 | 0                 | SS   | 0.1715    | 0.1601    | 0.7763     | 1.792    | 8                 | 0                 | SS   | 0.3122    | 0.2796    | 0.8225     | 1.796    |

| 8                 | 0                 | FF   | 0.1846    | 0.1243    | 0.7057     | 1.778    | 8                 |                   | FF   | 0.3447    | 0.3119    | 0.8095     | 1.791    |

| 8                 |                   | FS   | 0.1746    | 0.1143    | 0.7165     | 1.789    | 8                 |                   | FS   | 0.3091    | 0.2765    | 0.8297     | 1.796    |

| 8                 | 0                 | SF   | 0.1844    | 0.1247    | 0.6944     | 1.775    | 8                 | 0                 | SF   | 0.3462    | 0.3134    | 0.7975     | 1.789    |

|                   |                   |      |           |           |            |          |                   |                   |      |           |           |            |          |

|                   |                   |      |           |           |            |          |                   |                   |      |           |           |            |          |

|                   |                   |      |           |           |            |          |                   |                   |      |           |           |            |          |

| At 0.2 V, 100 uS  |                   |      |           |           |            |          | At 0.4 V, 100 uS  |                   |      |           |           |            |          |

| # of cells in LRS | # of cells in HRS |      | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) | # of cells in LRS |                   |      | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) |

| 0                 |                   | TT   | 0.1879    | 0.0592    | 0.4692     | 0.0057   | 0                 |                   | TT   | 0.3694    | 0.7192    | 0.429      | 0.0226   |

| 0                 |                   | SS   | 0.1847    | 0.0578    | 0.4557     | 0.0039   | 0                 | -                 | SS   | 0.3613    | 0.7045    | 0.4154     | 0.01328  |

| 0                 | 8                 | FF   | 0.1901    | 0.0602    | 0.4795     | 0.0077   | 0                 | 8                 | FF   | 0.3749    | 0.7293    | 0.4394     | 0.03421  |

| 0                 | -                 | FS   | 0.1843    | 0.0595    | 0.4509     | 0.0039   | 0                 | -                 | FS   | 0.3602    | 0.7223    | 0.4208     | 0.01415  |

| 0                 |                   | SF   | 0.1898    | 0.0583    | 0.4775     | 0.0075   | 0                 |                   | SF   | 0.3754    | 0.7062    | 0.4421     | 0.03053  |

| # of cells in LRS | # of cells in HRS |      | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) | # of cells in LRS |                   |      | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) |

| 1                 |                   | TT   | 0.1799    | 0.128     | 0.7177     | 1.786    | 1                 |                   | TT   | 0.3415    |           | 0.753      | 1.794    |

| 1                 |                   | SS   | 0.1742    | 0.1221    | 0.7217     | 1.788    | 1                 |                   | SS   | 0.3253    | 0.1851    | 0.7502     | 1.796    |

| 1                 |                   | FF   | 0.1842    | 0.1323    | 0.07172    | 1.78     | 1                 |                   | FF   | 0.3526    | 0.2105    | 0.7503     | 1.792    |

| 1                 |                   | FS   | 0.1739    | 0.1216    | 0.7316     |          | 1                 |                   | FS   | 0.3228    | 0.1831    | 0.7569     | 1.796    |

| 1                 |                   | SF   | 0.184     | 0.1325    | 0.7058     | 1.778    | 1                 |                   | SF   | 0.3538    | 0.2116    | 0.7403     | 1.791    |

| # of cells in LRS | # of cells in HRS |      | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) | # of cells in LRS |                   |      | BL_In (V) | SL_In (V) | InvOut (V) | Vout (V) |

| 8                 | -                 | TT   | 0.1782    | 0.1688    | 0.7741     | 1.79     | 8                 | -                 | TT   | 0.331     | 0.304     | 0.8207     | 1.797    |

| 8                 |                   | SS   | 0.1714    | 0.1632    | 0.7786     | 1.79     | 8                 |                   | SS   | 0.3116    | 0.285     | 0.825      | 1.798    |

| 8                 |                   | FF   | 0.1824    | 0.1732    | 0.7636     | 1.78     | 8                 |                   | FF   | 0.3443    | 0.3176    | 0.8125     | 1.795    |

| 8                 |                   | FS   | 0.1704    | 0.1613    | 0.7853     | 1.793    | 8                 |                   | FS   | 0.3084    | 0.2819    | 0.8349     | 1.798    |

| 8                 | 0                 | SF   | 0.1826    | 0.1736    | 0.7508     | 1.784    | 8                 | 0                 | SF   | 0.3458    | 0.3192    | 0.8003     | 1.794    |

Figure 18: Top-Level Simulation Results

From the top-level simulations, we were able to verify that our crossbar could perform form, write, read, and MAC operations on both the 0.2 V and 0.4 V compute crossbar designs. We verified this with extensive corner and error testing.

# 6 Project Outcomes

We have accomplished a lot with this project and have many different deliverables. The sections below will quickly highlight the outcome of each of them.

#### 6.1 FINAL 8x8 COMPUTE CROSSBAR

We were successfully able to push all individual components through the open-source analog design flow and verify their post-layout functionality. We were able to successfully do all operations on the crossbar that we were tasked with doing - form, write, read, and MAC. We were able to create a final layout of our design as well as hook up the two crossbars to the logic analyzer and external analog circuitry out to GPIOs for characterization. Unfortunately we were unable to pass precheck due to having outlying issues with the substrate connections on our PMOS devices, but also the ReRAM model itself still being in development. A status matrix of the work accomplished for our components can be seen in the figure below.

| Process Step   |           |             |             |             | Post Layout |

|----------------|-----------|-------------|-------------|-------------|-------------|

| Component      | Schematic | Simulation  | Layout      | DRC/LVS     | Simulations |

| Inverter       | Done      | Done        | Done        | Done        | Done        |

| Buffer (DAC)   | Done      | Done        | Done        | Done        | Done        |

| 2-1 MUX        | Done      | Done        | Done        | Done        | Done        |

| Level Shifters | Done      | Done        | Done        | Done        | Done        |

| OP-Amp         | Done      | Done        | Done        | Done        | Done        |

| TIA            | Done      | Done        | Done        | Done        | Done        |

| Inverting Amp  | Done      | Done        | Done        | Done        | Done        |

| 1-Bit ADC      | Done      | Done        | Done        | Done        | Done        |

| 1T1R Cell      | Done      | In-Progress | In-Progress | In-Progress | In-Progress |

| 8x8 Crossbar   | Done      | In-Progress | In-Progress | In-Progress | In-Progress |

| 8 Line WL      | Done      | Done        | Done        | Done        | Done        |

| 8 Line BL      | Done      | Done        | Done        | Done        | Done        |

| 8 Line SL In   | Done      | Done        | Done        | Done        | Done        |

| 8 Line SL out  | Done      | Done        | Done        | Done        | Done        |

| Top Level      | Done      | Done        | Done        | In-Progress | In-Progress |

| Figure 19 | 9: Stat | ıs Matrix | of Components |

|-----------|---------|-----------|---------------|

|-----------|---------|-----------|---------------|

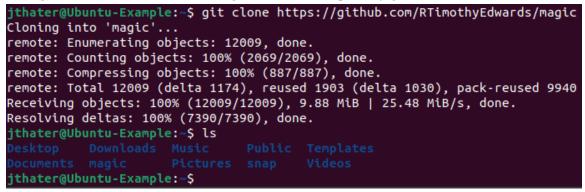

#### 6.2 GITHUB REPOSITORY

All of our components and their files are stored in a GitHub repository. These files include the schematics and layouts of each component. We also have the final top-level schematic and layout included in the repository as well. We also included all of the digital work that was done throughout the course of this project, such as the digital model, drivers, and C code. The link to the repository can be found here: https://github.com/Jthater1/ReRAM\_Crossbar\_Project

#### 6.3 POST-FABRICATION BRING-UP PLAN

A post-fabrication bring-up plan was created that detailed all of the steps that would be completed if our chip was fabricated once the outstanding issues were resolved. It includes how to test all of the external circuitry as well as how to test the compute crossbars. This bring-up plan can be found on our senior design website, but it is also included in appendix 8.1.4.

# 6.4 TUTORIAL DOCUMENTATION ON ANALOG DESIGN FLOW + OTHER DOCUMENTATION

While working on this project, we documented how we went through the open-source analog design flow. This work was compiled and edited into a tutorial document for the open-source analog design flow. This documentation is very detailed but thorough on all steps of the design process. The end result was a document that was 80 pages long. The documentation included sections on:

- Intro

- Environment setup

- Tool Installation

- Tool usage with example "hello world project" with inverter

- Integration of tools with SkyWater 130 nm Process

- Interfacing analog design with Caravel Harness

Along with this additional documentation was created for how to run precheck on an analog design along with documentation on the digital behavioral model that was created for this project. This documentation can be found on our project website.

# 7 Closing Material

#### 7.1 DISCUSSION

We were able to design a ReRAM crossbar that was able to perform form, write, read/MAC operations at a schematic level. We were also able to create a top-level layout that hooked two different compute crossbars to the Caravel Harness. In this Caravel Harness, we were able to hook up external analog circuitry that would be used for characterization if fabricated. Unfortunately, we were not able to have our design pass precheck and be ready for fabrication partially due to issues in our layout, but also outstanding issues with the ReRAM model currently used in this design flow.

We were able to create detailed tutorial documentation that outlined the entire open-source analog design flow. This documentation ended up being very long, but it will be very beneficial to people who utilize it in the future as it highlights all of the needed steps for analog design through eFabless. We struggled for a very long time - multiple months and hours and hours of troubleshooting - to figure out the design flow. So, by having it fully documented we hope to alleviate all of that possible frustration for future people.

The work we accomplished, plus all of the documentation we created should allow for a future senior design team to hit the ground running to fix our design and even make improvements to it.

#### 7.2 CONCLUSION

While we may not have been able to have our design ready for fabrication we still accomplished a lot of very good work. We were able to figure out the open-source analog design flow and thoroughly document it for future use here at ISU. We also were able to show that our design

worked at a schematic simulation level and even created a layout of how all of our designs would be hooked up to the Caravel Harness. The work we accomplished, plus all of the documentation we created it should allow for a future senior design team to hit the ground running to fix our design and even make improvements to it.

#### 7.3 References

- [1] A. Shafiee et al., "ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars," 2016 ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), Seoul, Korea (South), 2016, pp. 14-26, doi: 10.1109/ISCA.2016.12. https://ieeexplore.ieee.org/document/7551379

- [2] T. Chou, W. Tang, J. Botimer, and Z. Zhang, Electrical Engineering and computer science, <u>https://web.eecs.umich.edu/~zhengya/papers/chou\_micro19.pdf</u>.

- [3] T. Boucard, "Spotlight on Resistive Ram (reram) an interview with Weebit Nano," Yole Group, <u>https://www.yolegroup.com/player-interviews/spotlight-on-resistive-ram-reram</u> <u>-an-interview-with-weebit-nano/</u>.

- [4] "Sky130\_fd\_pr\_reram sky130 reram (Skywater provided)¶," sky130\_fd\_pr\_reram SKY130 ReRAM (SkyWater Provided) - SkyWater SKY130 PDK 0.0.0-22-g72df095 documentation.

[Online]. Available: https://sky130-fd-pr-reram.readthedocs.io/en/latest/technology\_specifications

html#forming

# 8 Appendices

#### 8.1 APPENDIX 1 - OPERATION MANUAL

For the operation of our project there are two parts. The first part is getting the pre-fabrication environment/files set up. The second part is the post-fabrication bring-up plan once our design has passed precheck and is sent back to us.

First, we will detail out the pre-fabrication stuff. Most of this information is pulled directly from the tutorial analog design flow documentation was created. To see the full version of this document check out our senior design website. Here, we will just include the setup of the environment and tools that are required to start working on the pre-fabrication side of our project.

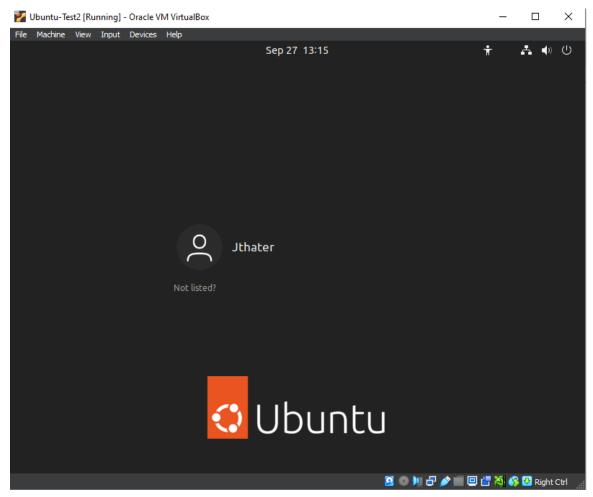

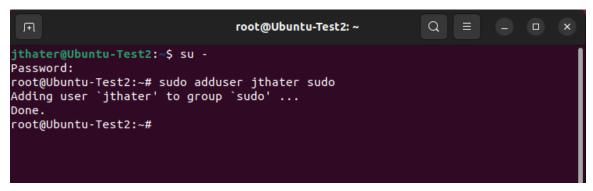

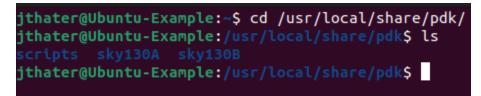

#### 8.1.1 Pre-Fabrication Environment Setup

This will provide a general guide on how to set up a virtual environment that will be able to house all the tools that are needed for the open-source analog design flow.

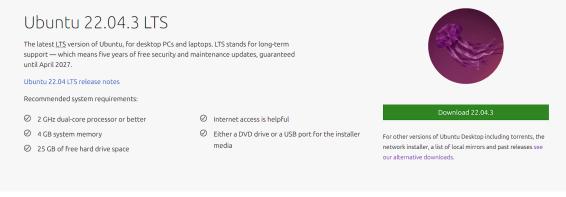

To start things things off, in order to do the analog design flow, it is *heavily recommended* to use a Linux system or MAC system. It may be possible to use a Windows operating system, but certain software may be out of date or not available at all.

The rest of this section will cover how to download and install a Ubuntu VM with the specific hardware requirements needed for this analog design flow. If you do not plan to use an Ubuntu VM for your environment, then you can safely skip this section. However, be sure that your environment will be able to run all the tools that are needed.

It is recommended to use Virtual Box for your VM. Below is the link to download Virtual Box: <u>https://www.virtualbox.org/wiki/Downloads</u>

Once you have Virtual Box downloaded, it is time to set up the Ubuntu VM. First, head to the webpage linked below. Ubuntu Desktop Virtual Machine Set Up: <u>https://ubuntu.com/download/desktop</u>

Once there, download an Ubuntu image. It shouldn't matter which one you choose; just make sure it is past Ubuntu 20 (which all of them on the download page should be anyway). For this example, Ubuntu 22.04.3 was used, which can be seen below.

Figure 20: Ubuntu Image

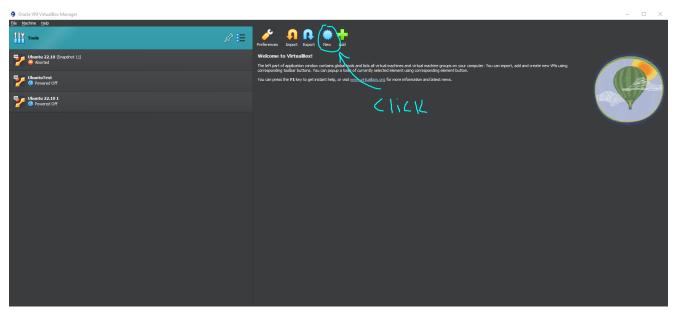

This ISO is a few GB, so it may take a bit to install. Once it is installed, you can head over to Virtual Box. Once in Virtual Box, you should see a screen similar to the one seen below. To begin setting up the virtual machine, click on "New" as seen in the figure below.

Figure 21: Virtual Box Setup

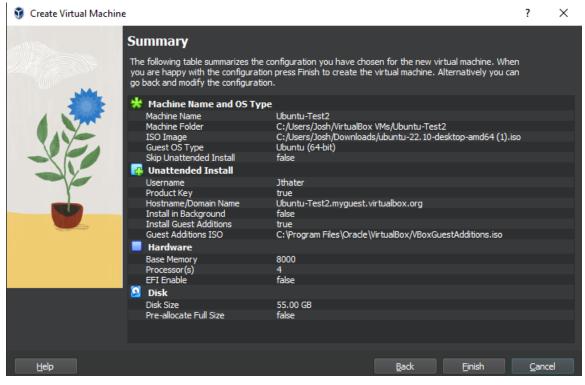

Once that is done, simply give a name to your virtual machine and select the ISO image you just downloaded (the ISO should be in your downloads directory). If you did all that correctly, it should look something like this.

| 🐧 Cri | ate Virtual Machin | e                  |                                                                                                                                                                                                                      | ?            | $\times$ |

|-------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|

|       |                    | Virtual            | machine Name and Operating System                                                                                                                                                                                    |              |          |

|       |                    | used throug        | se a descriptive name and destination folder for the new virtual machine. The name you d<br>hout VirtualBox to identify this machine. Additionally, you can select an ISO image which r<br>e guest operating system. |              |          |

|       |                    | <u>N</u> ame:      | Ubuntu_Example                                                                                                                                                                                                       |              | *        |

| (     |                    | <u>F</u> older:    | C:\Users\Josh\VirtualBox VMs                                                                                                                                                                                         |              |          |

| -     |                    | <u>I</u> SO Image: | C:\Users\Josh\Downloads\ubuntu-22.04.3-desktop-amd64.iso                                                                                                                                                             |              |          |

| -     |                    | Edition:           |                                                                                                                                                                                                                      |              |          |

|       |                    | <u>T</u> ype:      |                                                                                                                                                                                                                      |              | 64       |

|       |                    | <u>V</u> ersion:   |                                                                                                                                                                                                                      |              |          |

|       |                    |                    | Skip Unattended Installation                                                                                                                                                                                         |              |          |

|       |                    |                    | Detected OS type: Ubuntu (64-bit). This OS type can be installed unattendedly. The<br>start after this wizard is closed.                                                                                             | install w    | ill      |

| H     | elp                |                    | Expert Mode Back Next                                                                                                                                                                                                | <u>C</u> anc | el       |

Figure 22: VM Name

Once this is done, click next. On the following screen, you can change the username and password of your machine. It is recommended that you change these settings so that you can get sudo access on your machine. Don't worry about changing the hostname or domain name. Finally, on this screen, make sure to select the box for "Guest Additions"; this adds a bunch of

quality-of-life features, such as dynamic screen resolution. Once this is all done, it should look something like this.

| 🧿 Create Virtual Machir | ie                                                                                                                                                                                                                                |                                 |                            | ?                 | $\times$ |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------|-------------------|----------|--|--|--|